# Software Implementations of Polynomial Multiplications for Lattice-Based Cryptosystems

Vincent Bert Hwang

# Software Implementations of Polynomial Multiplications for Lattice-Based Cryptosystems

Proefschrift ter verkrijging van de graad van doctor aan de Radboud Universiteit Nijmegen op gezag van de rector magnificus **TODO:** name , volgens besluit van het college voor promoties in het openbaar te verdedigen op

TODO: date

**TODO:** time

door

Vincent Bert Hwang

geboren op **TODO**: date te **TODO**: location

#### Promotor

Prof. dr. Peter Schwabe

### Copromotor

Prof. dr. Bo-Yin Yang Academia Sinica, Taiwan

### Manuscriptcommissie

Prof. dr. Lejla Batina

Dr. ing. Thomas Pöppelmann Infineon Technologies AG, Duitsland

Prof. dr. ing. Tim Güneysu Ruhr-Universität Bochum, Duitsland

Prof. dr. ir. Ingrid Verbauwhede Katholieke Universiteit Leuven, België

Dr. Francisco Rodríguez-Henríquez Technology Innovation Institute, Verenigde Arabische Emiraten

## Contents

| Li | st of        | Algorithms                                    | ix   |

|----|--------------|-----------------------------------------------|------|

| Li | st of        | Figures                                       | xiii |

| Li | st of        | Listings                                      | xvii |

| Li | st of        | Tables                                        | xix  |

| 1  | Intr         | roduction                                     | 1    |

|    | 1.1          | Subject of Research                           | 1    |

|    | 1.2          | Contributions of This Thesis                  | 7    |

|    | 1.3          | Research Data Management                      | 14   |

|    | 1.4          | Related Survey Works                          | 14   |

|    | 1.5          | Additional Publications                       | 15   |

|    | 1.6          | Structure of This Thesis                      | 17   |

| Ι  | $\mathbf{M}$ | athematical Foundations                       | 19   |

| 2  | Alg          | ebraic Background                             | 21   |

|    | 2.1          | Rings and Fields                              | 21   |

|    | 2.2          |                                               | 25   |

| 3  | Mo           | dular Multiplications                         | 31   |

|    | 3.1          | Numbers                                       | 31   |

|    | 3.2          | Integer Approximations and Modular Reductions | 32   |

|    | 3.3          | Montgomery Multiplication                     | 35   |

|    | 3.4          | Barrett Multiplication                        | 37   |

|    | 3.5          | Plantard Multiplication                       | 38   |

vi CONTENTS

|          | 3.6  | Floor and Round of Fractions                         | 42  |

|----------|------|------------------------------------------------------|-----|

| 4        | Fast | Homomorphisms                                        | 45  |

|          | 4.1  | Karatsuba and Toom-Cook                              | 45  |

|          | 4.2  | Discrete Fourier Transform                           | 46  |

|          | 4.3  | Cooley-Tukey Fast Fourier Transform                  | 49  |

|          | 4.4  | Bruun's Fast Fourier Transform                       | 51  |

|          | 4.5  | Good–Thomas Fast Fourier Transform                   | 52  |

|          | 4.6  | Vector–Radix Fast Fourier Transform                  | 54  |

|          | 4.7  | Rader's Fast Fourier Transform                       | 54  |

|          | 4.8  | Comparisons                                          | 55  |

| 5        | Coe  | fficient Ring Embedding                              | 59  |

|          | 5.1  | Localization                                         | 59  |

|          | 5.2  | Schönhage's and Nussbaumer's Fast Fourier Transforms | 61  |

|          | 5.3  | Coefficient Ring Switching                           | 64  |

|          | 5.4  | Comparisons                                          | 65  |

| 6        | The  | Choices of Polynomial Moduli                         | 69  |

|          | 6.1  | Embedding                                            | 69  |

|          | 6.2  | Twisting                                             | 70  |

|          | 6.3  | Truncation                                           | 71  |

|          | 6.4  | Incomplete Transformation and Striding               | 74  |

|          | 6.5  | Toeplitz Matrix-Vector Product                       | 75  |

| 7        | Vec  | torization                                           | 81  |

|          | 7.1  | Vectorization-Friendliness                           | 81  |

|          | 7.2  | Permutation-Friendliness                             | 82  |

|          | 7.3  | Vectorizing Toeplitz Matrix-Vector Product           | 85  |

|          | 7.4  | Choosing Homomorphisms for Vectorization             | 86  |

| II       | G    | eneral Guide for Optimizations                       | 89  |

| 8        | Plat | tforms                                               | 91  |

| <u> </u> | 8.1  | Instruction Set Architectures and Extensions         | 91  |

|          |      | Processors                                           | 115 |

CONTENTS vii

| 9         | _               | lementations of Modular Multiplications (Mulmod.) and Quo |     |

|-----------|-----------------|-----------------------------------------------------------|-----|

|           | <b>tien</b> 9.1 | Multiplications                                           | 123 |

|           | 9.1             | Modular Multiplications                                   | 123 |

|           | 9.2             |                                                           | 128 |

|           | 9.5             | Quotients                                                 | 149 |

| 10        |                 | eral Guide for Optimizing Transformations                 | 161 |

|           |                 | General Optimization Strategies                           | 161 |

|           |                 | Isomorphisms                                              | 164 |

|           | 10.3            | Monomorphisms That Are Not Isomorphisms                   | 172 |

| II        | I A             | Applications to Lattice-Based Cryptosystems               | 177 |

| 11        | Ben             | chmarking Methodology                                     | 179 |

|           | 11.1            | Cortex-M3 and Cortex-M4                                   | 179 |

|           |                 | Cortex-A72 and Firestorm                                  | 181 |

|           | 11.3            | Haswell                                                   | 182 |

| <b>12</b> |                 | thium                                                     | 183 |

|           |                 | Specification                                             | 183 |

|           |                 | Optimization Guide for Polynomial Arithmetic              | 186 |

|           |                 | Reviewing and Improving Cortex-M3 Implementations         | 188 |

|           |                 | Reviewing and Improving Cortex-M4 Implementations         | 193 |

|           |                 | Reviewing and Improving Armv8-A Neon Implementations      | 195 |

|           | 12.6            | Reviewing AVX2 Implementations                            | 197 |

| <b>13</b> | Kyb             | er                                                        | 199 |

|           |                 | Specification                                             | 199 |

|           |                 | Optimization Guide for Polynomial Arithmetic              | 202 |

|           |                 | Reviewing and Improving Cortex-M3 Implementations         | 203 |

|           |                 | Reviewing and Improving Cortex-M4 Implementations         | 206 |

|           |                 | Reviewing and Improving Armv8-A Neon Implementations      | 208 |

|           | 13.6            | Reviewing and Improving AVX2 Implementations              | 213 |

| 14        | NTI             |                                                           | 217 |

|           |                 | Specification                                             | 217 |

|           |                 | Optimization Guide for Polynomial Arithmetic              | 219 |

|           |                 | Reviewing Cortex-M4 Implementations                       | 223 |

|           | 14.4            | Reviewing and Improving Armv8-A Neon Implementations      | 225 |

|           | 14.5            | Reviewing AVX2 Implementations                            | 229 |

viii CONTENTS

| <b>15</b>    | NTRU Prime                                                   | 231 |

|--------------|--------------------------------------------------------------|-----|

|              | 15.1 Specification                                           | 231 |

|              | 15.2 Optimization Guide for Polynomial Arithmetic            | 235 |

|              | 15.3 Reviewing Cortex-M4 Implementations                     | 236 |

|              | 15.4 Reviewing and Improving Armv8-A Neon Implementations $$ | 238 |

|              | 15.5 Reviewing and Improving AVX2 Implementations            | 248 |

| 16           | Saber                                                        | 251 |

|              | 16.1 Specification                                           | 251 |

|              | 16.2 Optimization Guide for Polynomial Arithmetic            | 253 |

|              | 16.3 Reviewing and Improving Cortex-M3 Implementations       | 257 |

|              | 16.4 Reviewing Cortex-M4 Implementations                     | 260 |

|              | 16.5 Reviewing Armv8-A Neon Implementations                  | 264 |

|              | 16.6 Reviewing AVX2 Implementations                          | 266 |

| Bi           | bliography                                                   | 269 |

| A            | On Formal Verification                                       | 293 |

|              | A.1 Paper: Formal Verification of Float                      | 293 |

|              | A.2 Paper: Verified NTT Multiplications                      | 311 |

| В            | Large Integer Multiplications                                | 353 |

|              | B.1 Paper: Integer Multiplications using NTTs                | 353 |

| $\mathbf{C}$ | Research Data Management                                     | 379 |

| D            | Index                                                        | 381 |

| Su           | mmary                                                        | 387 |

| Sa           | menvatting                                                   | 389 |

| 總            | 结                                                            | 391 |

| Cı           | urriculum Vitae                                              | 393 |

# List of Algorithms

| Chapter           | 7: Vectorization                                                                          | 81  |

|-------------------|-------------------------------------------------------------------------------------------|-----|

| 7.1               | Applying a $4 \times 4$ Toeplitz matrix with vector-by-scalar multiplication instructions | 86  |

| Chapter<br>tients | •                                                                                         | 123 |

| 9.1               | 32-bit Montgomery multiplication in Armv7-M                                               | 134 |

| 9.2               | Emulation of smlal (smull) with mul in Armv7-M                                            | 134 |

| 9.3               | Macros sbsmlal (sbsmull) emulating smull and smlal with                                   | 105 |

| 0.4               | mul/mla                                                                                   | 135 |

| 9.4               | Constant-time 32-bit Montgomery multiplication in Armv7-M.                                | 135 |

| 9.5               | 16-bit Montgomery multiplication with mul/mla in Armv7-M.                                 | 136 |

| 9.6               | 16-bit Montgomery multiplication with DSP instructions in                                 |     |

|                   | Armv7E-M                                                                                  | 136 |

| 9.7               | Standard (floor) 32-bit Barrett multiplication in Armv7E-M.                               | 137 |

| 9.8               | Standard 32-bit Barrett multiplication (reduction) for 16-bit                             |     |

|                   | inputs and 32-bit constant with DSP instructions in Armv7E-M.                             | 137 |

| 9.9               | 32-bit high multiplication with the integer approximation []                              |     |

|                   | in Armv7-M                                                                                | 138 |

| 9.10              | Macro smmulr_approx implementing the 32-bit high multipli-                                |     |

|                   | cation with integer approximation $[]_b$ ( $_b[]$ ) in Armv7-M                            | 138 |

| 9.11              | Approximate variant of 32-bit Barrett multiplication in                                   |     |

|                   | Armv7-M                                                                                   | 139 |

| 9.12              | Standard (floor) 16-bit Barrett multiplication in Armv7-M                                 | 139 |

| 9.13              | Standard (floor) 16-bit Barrett multiplication with DSP in-                               |     |

|                   | structions in Armv7E-M                                                                    | 140 |

|                   |                                                                                           |     |

| 9.14    | 16-bit Plantard multiplication in Armv7-M                                  | 140 |

|---------|----------------------------------------------------------------------------|-----|

| 9.15    | 16-bit Plantard multiplication with DSP instructions in                    |     |

|         | Armv7E-M                                                                   | 141 |

| 9.16    | 32-bit Plantard multiplication with DSP instructions in                    |     |

|         | Armv7E-M                                                                   | 141 |

| 9.17    | Montgomery multiplication in Armv8-A Neon                                  | 144 |

| 9.18    | w-bit Barrett reduction for $w \ge \log_2 \mathtt{R}$ in Armv8-A Neon      | 144 |

| 9.19    | Barrett multiplication in Neon                                             | 145 |

| 9.20    | 16-bit Montgomery multiplication in AVX2                                   | 146 |

| 9.21    | 32-bit Montgomery multiplication in AVX2                                   | 147 |

| 9.22    | Standard w-bit Barrett reduction for $17 \le w < 32$ (floor variant        |     |

|         | for $16 \le w < 32$ ) in AVX2                                              | 148 |

| 9.23    | Standard 15-bit (floor in the case of 16-bit) Barrett multipli-            |     |

|         | cation in AVX2                                                             | 148 |

| 9.24    | Armv7-M implementation of $Compress_d$ for $d = 1,, 7.$                    | 153 |

| 9.25    | Armv7-M implementation of $Compress_d$ for $d = 10, 11. \dots$             | 153 |

| 9.26    | Armv7E-M implementation of $\mathtt{Compress}_d$ for $d=1,\ldots,10\ldots$ | 154 |

| 9.27    | Armv7E-M implementation of Compress <sub>d</sub> for $d = 1,, 11$          | 154 |

| 9.28    | Armv8-A Neon implementation of Compress <sub>1</sub>                       | 156 |

| 9.29    | Armv8-A Neon implementation of Compress <sub>4</sub>                       | 156 |

| 9.30    | Armv8-A Neon implementation of Compress <sub>5</sub>                       | 156 |

| 9.31    | Armv8-A Neon implementation of Compress <sub>{10,11}</sub>                 | 157 |

| 9.32    | AVX2 implementation of Compress <sub>1</sub>                               | 158 |

| 9.33    | AVX2 implementation of Compress <sub>4</sub>                               | 158 |

| 9.34    | AVX2 implementation of Compress <sub>5</sub>                               | 159 |

| 9.35    | AVX2 implementation of $Compress_d$ for $d = 10, 11. \dots$                | 159 |

| Chapter | 10: General Guide for Optimizing Transformations                           | 161 |

| 10.1    | Pseudocode of Rader-p                                                      | 170 |

| 10.2    | Pseudocode of truncated Rader-p                                            | 172 |

| 10.3    | Negacyclic shift $i = 1,, 7$ coefficients with Armv8-A Neon                | 174 |

| 10.4    | Negacyclic shift $i=1,\ldots,15$ coefficients with AVX2                    | 175 |

| Chapter | 12: Dilithium                                                              | 183 |

| 12.1    | Dilithium key generation                                                   | 184 |

| 12.2    | Dilithium signature generation                                             | 185 |

| 12.3    | Dilithium signature verification                                           | 186 |

| LIST | OF | AL | GO | RI' | $\Gamma H M$ | IS |

|------|----|----|----|-----|--------------|----|

|      |    |    |    |     |              |    |

|   | ٠ |

|---|---|

| v |   |

| Λ |   |

|   |   |

| Chapter | Chapter 13: Kyber 199                                                |             |  |

|---------|----------------------------------------------------------------------|-------------|--|

| 13.1    | Kyber PKE key generation                                             | 200         |  |

| 13.2    | Kyber PKE encryption                                                 | 201         |  |

| 13.3    | Kyber PKE decryption                                                 | 201         |  |

| Chapter | 14: NTRU                                                             | 217         |  |

| 14.1    | NTRU Key Generation                                                  | 218         |  |

| 14.2    | NTRU CPA Encryption                                                  | 218         |  |

| 14.3    | NTRU CPA Decryption                                                  | 219         |  |

| Chapter | 15: NTRU Prime                                                       | 231         |  |

| 15.1    | Streamlined NTRU Prime key generation                                | 232         |  |

| 15.2    | Streamlined NTRU Prime encryption                                    | 232         |  |

| 15.3    | Streamlined NTRU Prime decryption                                    | 233         |  |

| 15.4    | NTRU LPrime key generation                                           | 234         |  |

| 15.5    | NTRU LPrime encryption                                               | 234         |  |

| 15.6    | NTRU LPrime decryption                                               | 235         |  |

| 15.7    | Radix-2 butterfly with symbolic root $x^2$                           | 242         |  |

| Chapter | 16: Saber                                                            | <b>251</b>  |  |

| 16.1    | Saber PKE key generation.                                            | 252         |  |

| 16.2    | Saber PKE encryption                                                 | 252         |  |

| 16.3    | Saber PKE decryption                                                 | 253         |  |

| Chapter | A: On Formal Verification                                            | <b>2</b> 93 |  |

| A.1     | Falcon key generation from the reference implementation              | 294         |  |

| A.2     | Falcon signature generation from the reference implementation.       |             |  |

| A.3     | Falcon signature verification                                        | 296         |  |

| A.4     | Emulated C implementation of floating-point multiplication in Falcon | 300         |  |

| A.5     | Range arithmetic of floating-point multiplication.                   | 306         |  |

| A.6     | Range arithmetic of floating-point addition/subtraction              | 306         |  |

| 11.0    | reange arrenment of noating-point addition, subtraction              | 500         |  |

| Chapter | B: Large Integer Multiplications                                     | 353         |  |

| B.1     | Montgomery squaring using NTTs                                       | 364         |  |

| B.2     | Montgomery multiplication using NTTs                                 | 364         |  |

| В.3 | $(\log_2 R)$ -bit Barrett reduction on Cortex-M3             | 373 |

|-----|--------------------------------------------------------------|-----|

| B.4 | 16-bit Montgomery multiplication on Cortex-M3                | 374 |

| B.5 | FNT reduction on Cortex-M3                                   | 374 |

| B.6 | Barrett multiplication on Cortex-M55                         | 374 |

| B.7 | Conditional move on Cortex-M3                                | 377 |

| B.8 | Overlapping-friendly conditional accumulation on Cortex-M55. | 377 |

## List of Figures

| Chapter | 3: Modular Multiplications                                                                                       | 31 |  |

|---------|------------------------------------------------------------------------------------------------------------------|----|--|

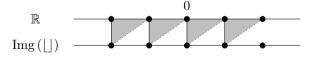

| 3.1     | The floor function $\lfloor \rfloor$                                                                             | 33 |  |

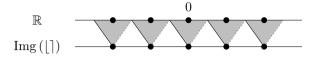

| 3.2     | The rounding-half-up function []                                                                                 | 34 |  |

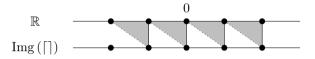

| 3.3     | The ceiling function $[]$                                                                                        | 34 |  |

| 3.4     | Rounding-to-the-nearest-even                                                                                     | 35 |  |

| Chapter | 4: Fast Homomorphisms                                                                                            | 45 |  |

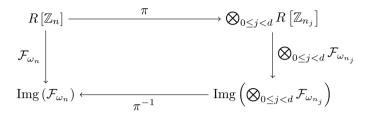

| 4.1     | Commutative diagram of Good–Thomas FFT in the group algebra view                                                 | 53 |  |

| Chapter | 6: The Choices of Polynomial Moduli                                                                              | 69 |  |

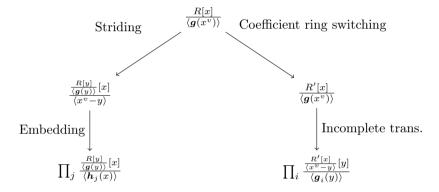

| 6.1     | Overview of approaches built upon coefficient ring switching, embedding, incomplete transformation, and striding | 75 |  |

| Chapter | 7: Vectorization                                                                                                 | 81 |  |

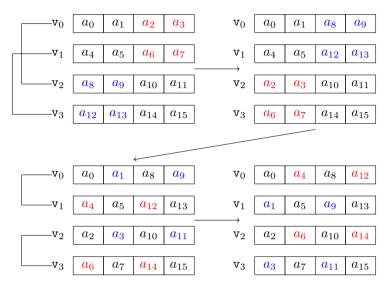

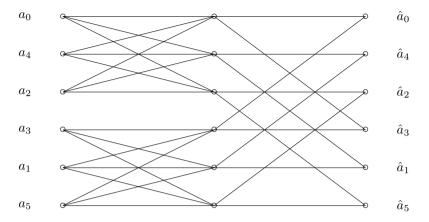

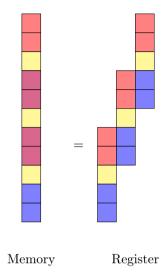

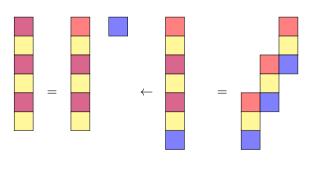

| 7.1     | Top-down transposition of a $4 \times 4$ matrix                                                                  | 83 |  |

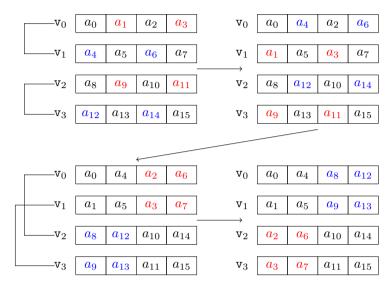

| 7.2     | Bottom-up transposition of a $4 \times 4$ matrix                                                                 | 84 |  |

|         |                                                                                                                  |    |  |

| Chapter | 8: Platforms                                                                                                     | 91 |  |

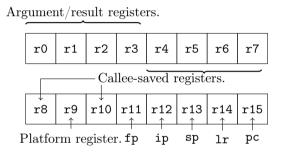

| 8.1     | General-purpose registers in Armv7-M architecture                                                                | 92 |  |

xiv LIST OF FIGURES

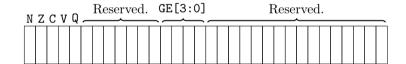

| 8.2    | Application program status register in Armv7-M           | 98         |

|--------|----------------------------------------------------------|------------|

| 8.3    | Floating-point registers in FPv4-SP extension Armv7-M    | 99         |

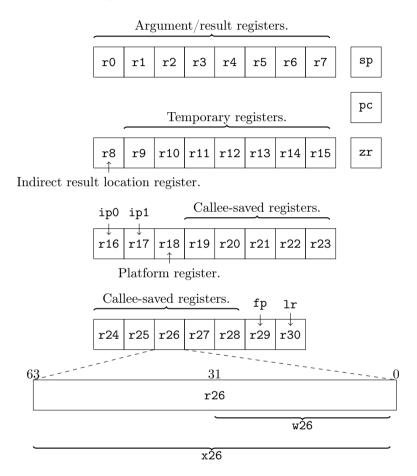

| 8.4    | General-purpose registers in Armv8-A                     | 101        |

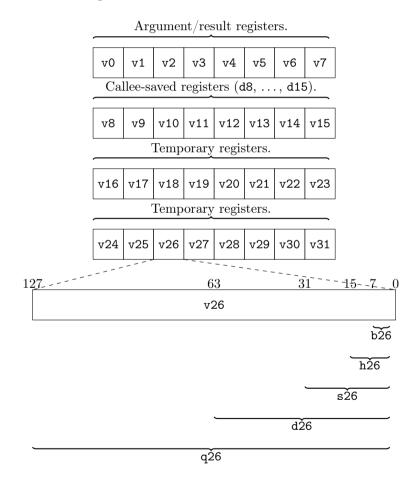

| 8.5    | SIMD registers in Armv8-A Neon                           | 102        |

| 8.6    | General-purpose registers x86-64                         | 111        |

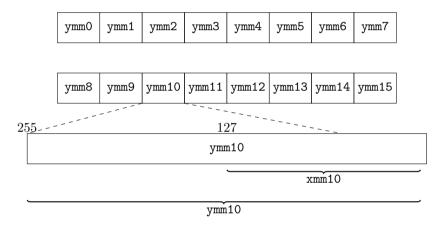

| 8.7    | SIMD registers in AVX2                                   | 112        |

| Chapte | er 10: General Guide for Optimizing Transformations      | 161        |

| 10.1   | Instruction scheduling of a loop.                        | 164        |

| 10.2   |                                                          | 165        |

| 10.3   |                                                          | 167        |

| 10.4   |                                                          | 168        |

| 10.5   | · · · · · · · · · · · · · · · · · · ·                    | 169        |

| 10.6   |                                                          | 173        |

| 10.7   |                                                          | . 173      |

| Chapte | er 15: NTRU Prime                                        | 231        |

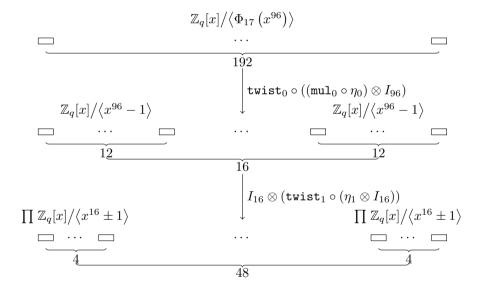

| 15.1   | · · · · · · · · · · · · · · · · · · ·                    | 0.4.4      |

| 15.2   | 128-bit SIMD register view in Armv8-A Neon               | 244<br>249 |

| Chapte | er A: On Formal Verification                             | 293        |

| A.1    | Cooley-Tukey (CT) Butterfly                              | 318        |

| A.2    |                                                          | 318        |

| A.3    |                                                          | 319        |

| A.4    | CryptoLine syntax                                        | 321        |

| A.5    | CryptoLine expressions and predicates                    | 322        |

| A.6    | Before SSA transformation                                | 326        |

| A.7    | After SSA transformation                                 | 326        |

| A.8    | Workflow of verifying AVX2 implementation for Kyber NTT. | 333        |

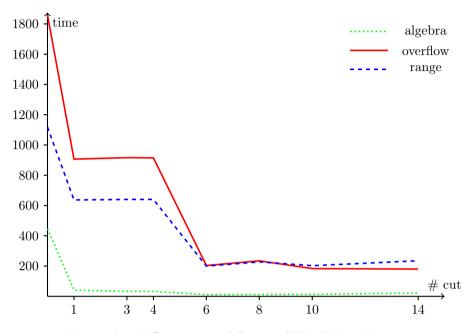

| A.9    | Effectiveness of Cuts in AVX2 Kyber NTT                  | 350        |

| Chapte | er B: Large Integer Multiplications                      | 353        |

| LIST OF FIGURES | XV |

|-----------------|----|

|                 |    |

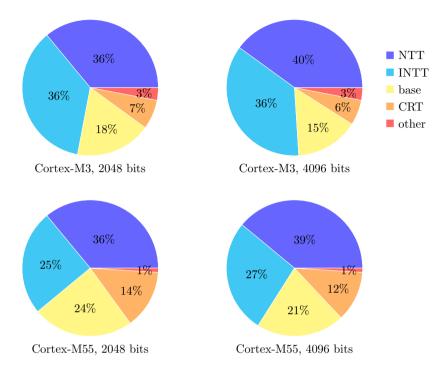

| B.1 | Clock cycles spent on the subroutines of a single modular mul- |     |

|-----|----------------------------------------------------------------|-----|

|     | tiplication                                                    | 373 |

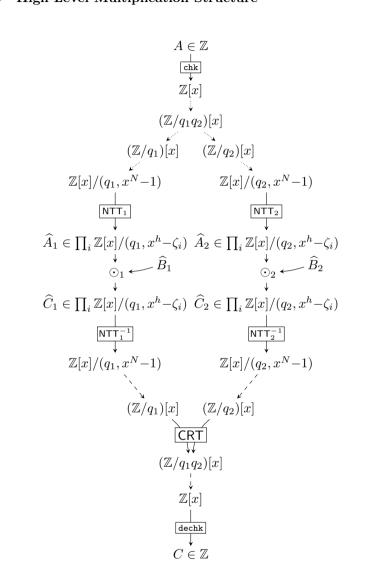

| B.2 | High-level structure of our integer multiplication algorithm   | 376 |

## List of Listings

| Chapter          | 1: Introduction                                                                                                                                                                                               | 1   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1<br>1.2       | Matrix multiplication with accumulation of dimension $I \times J \times K$ .<br>Matrix multiplication with accumulation of dimension $I \times J \times K$                                                    | 5   |

|                  | iterating in the order $i, j, k$ with Armv8-A Neon intrinsics in C.                                                                                                                                           | 6   |

| 1.3              | Matrix multiplication with accumulation of dimension $\mathbb{I} \times \mathbb{J} \times \mathbb{K}$ iterating in the order $i, k, j$ with Armv8-A Neon intrinsics in C.                                     | 7   |

| Chapter<br>tient | 9: Implementations of Modular Multiplications and Quo-<br>s                                                                                                                                                   | 123 |

| 9.1              | C implementations of $\mathtt{Compress}_{\{1,4,5\}}$ for $\mathtt{a} \in \left[-\frac{q}{2}, \frac{q}{2}\right) \cap \mathbb{Z}$ where $315 = \left\lfloor \frac{2^{20}}{q} \right\rfloor$ , and $q = 3329$   | 152 |

| 9.2              | C implementations of $Compress_{\{10,11\}}$ for $\mathbf{a} \in \left[-\frac{q}{2}, \frac{q}{2}\right) \cap \mathbb{Z}$ where $1290167 = \left\lfloor \frac{2^{32}}{q} \right\rfloor$ , and $q = 3329.\ldots$ | 153 |

| Chapter          | · 14: NTRU                                                                                                                                                                                                    | 217 |

| 14.1             | ( ) / )                                                                                                                                                                                                       | 221 |

| 14.2             | C implementation of bitsliced multiplication of elements in $\mathbb{Z}_3 = \{-1, 0, 1\}$ based on [BBC <sup>+</sup> 20]                                                                                      | 221 |

| Chapter          | A: On Formal Verification                                                                                                                                                                                     | 293 |

| A.1<br>A.2       | Our C program testing if the input is small enough Our C program testing if there is an input leading to incorrect                                                                                            | 302 |

|                  |                                                                                                                                                                                                               | 302 |

## List of Tables

| Chapter    | r 1: Introduction                                                                                                                                           | 1        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1<br>1.2 | Scope of this thesis on Cortex-M3 and Cortex-M4 Scope of this thesis on Cortex-A72, Firestorm, and Haswell                                                  | 3        |

| Chapter    | r 4: Fast Homomorphisms                                                                                                                                     | 45       |

| 4.1        | Summary of the number of arithmetic and conditions of $\mathcal{F}_{\omega_n}$ and $\mathcal{F}_{\omega_n,\zeta\neq 1}$                                     | 49       |

| 4.3        | Good–Thomas, vector-radix, Rader, and Toom–Cook Overview of the defining conditions of Cooley–Tukey, Bruun, Good–Thomas, vector-radix, Rader, and Toom–Cook | 56<br>57 |

| Chapter    | r 5: Coefficient Ring Embedding                                                                                                                             | 59       |

| 5.1        | Overview of radix-2 Schönhage's and Nussbaumer's FFTs                                                                                                       | 64       |

| 5.2        | Overview of optimal radix-2 Schönhage's and Nussbaumer's FFTs                                                                                               | 64       |

| 5.3<br>5.4 | Overview of the cost of coefficient ring embedding Overview of the arithmetic cost of Schönhage's/Nussbaumer's and Cooley-Tukey FFTs                        | 66<br>67 |

| Chapter    | r 8: Platforms                                                                                                                                              | 91       |

| 8.1        | Memory operations in Armv7-M                                                                                                                                | 93       |

xx LIST OF TABLES

| 8.2  | 8-bit parallel additions and subtractions in the DSP extension of Armv7E-M | 94  |

|------|----------------------------------------------------------------------------|-----|

| 8.3  | 16-bit parallel additions and subtractions in the DSP exten-               | 01  |

| 0.0  | sion of Armv7E-M                                                           | 95  |

| 8.4  | 16-bit crossed additions and subtractions in the DSP extension             |     |

|      | of Armv7E-M                                                                | 95  |

| 8.5  | Signed 16-bit multiplications in the DSP extension of                      |     |

|      | Armv7E-M                                                                   | 96  |

| 8.6  | Signed dual 16-bit multiplications in the DSP extension of                 |     |

|      | Armv7E-M                                                                   | 96  |

| 8.7  | Signed wide 16-bit multiplications in the DSP extension of                 |     |

|      | Armv7E-M.                                                                  | 97  |

| 8.8  | Signed most significant-word multiplications in the DSP ex-                |     |

|      | tension of Armv7E-M                                                        | 97  |

| 8.9  | Floating-point transferring operations in the FPv4-SP of                   |     |

|      |                                                                            | 100 |

| 8.10 | Summary of operands of transferring operations in Armv8-A                  |     |

|      |                                                                            | 103 |

| 8.11 | 1                                                                          | 104 |

| 8.12 | Summary of operands of permutations in Armv8-A Neon                        | 104 |

| 8.13 | Summary of operands of additions and subtractions in                       |     |

|      |                                                                            | 105 |

| 8.14 | Summary of operands of widening and narrowing operations                   |     |

|      |                                                                            | 106 |

| 8.15 | v i                                                                        | 106 |

| 8.16 |                                                                            | 107 |

| 8.17 | Summary of operands of bit-field operations in Armv8-A Neon.               |     |

| 8.18 | Summary of operands of counting operations in Armv8-A Neon.                | 108 |

| 8.19 | v i                                                                        | 108 |

| 8.20 | Summary of operands of left-shifts in Armv8-A Neon                         | 109 |

| 8.21 | Summary of operands of multiplications in Armv8-A Neon                     | 110 |

| 8.22 | Summary of operands of permutations in AVX2                                | 113 |

| 8.23 | Summary of operands of additions and subtractions in AVX2.                 | 113 |

| 8.24 | Summary of operands of bitwise operations in AVX2                          | 114 |

| 8.25 | Summary of operands of shifts in AVX2                                      | 114 |

| 8.26 | Summary of operands of multiplications in AVX2                             | 115 |

| 8 27 | Summary of arithmetic instruction timings on Cortex-M3                     | 116 |

LIST OF TABLES xxi

| Chapter | 9: Implementations of Modular Multiplications and Quo-                                                                                                   |     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| tients  | 5                                                                                                                                                        | 123 |

| 9.1     | Overview of the available multiplications in Armv7-M,                                                                                                    |     |

|         | Armv7E-M, Armv8 Neon, and AVX2                                                                                                                           | 124 |

| 9.2     | Multiplications in Armv7E-M                                                                                                                              | 126 |

| 9.3     | Multiplications in Armv8-A Neon                                                                                                                          | 127 |

| 9.4     | Multiplications in AVX2                                                                                                                                  | 127 |

| 9.5     | Overview of the variants of Barrett multiplications                                                                                                      | 130 |

| 9.6     | Overview of multiplications used in Montgomery multiplications.                                                                                          | 132 |

| 9.7     | Overview of multiplications used in Barrett and Plantard multiplications                                                                                 | 133 |

| 9.8     | Overview of 32-bit modular multiplications with 32-bit input                                                                                             | 100 |

| 0.0     | values on Cortex-M3                                                                                                                                      | 142 |

| 9.9     | Overview of 16-bit modular multiplications with 16-bit input                                                                                             |     |

|         | values on Cortex-M3                                                                                                                                      | 142 |

| 9.10    | Overview of 32-bit modular multiplications with 32-bit input                                                                                             |     |

|         | values on Cortex-M4                                                                                                                                      | 143 |

| 9.11    | Overview of 16-bit modular multiplications with packed 16-bit                                                                                            |     |

|         | input values on Cortex-M4                                                                                                                                | 143 |

| 9.12    | Overview of Montgomery and Barrett reductions/multiplica-                                                                                                |     |

|         | tions with Armv8-A Neon                                                                                                                                  | 145 |

| 9.13    | Overview of Montgomery and Barrett reductions/multiplica-                                                                                                |     |

|         | tions with AVX2                                                                                                                                          | 149 |

| 9.14    | Smallest Rs implementing $\left\lfloor \frac{a2^d}{q} \right\rfloor = \left\lfloor \frac{a \lfloor 2^d R/q \rfloor}{R} \right\rfloor$ for various $d$ 's | 151 |

| 9.15    | Overview of a single $Compress_d$ for $d = 1, 4, 5, 10, 11$ on                                                                                           |     |

| 0.10    | Cortex-M3 and Cortex-M4.                                                                                                                                 | 155 |

| 9.16    | Overview of $Compress_d$ for $d = 1, 4, 5, 10, 11$ with Armv8-A Neon.                                                                                    |     |

| 9.17    | Overview of $Compress_d$ for $d=1,4,5,10,11$ with AVX2                                                                                                   | 159 |

| Chapter | 10: General Guide for Optimizing Transformations                                                                                                         | 161 |

| 10.1    | Registers for scalar arithmetic                                                                                                                          | 162 |

| 10.2    | Registers for vector arithmetic                                                                                                                          | 162 |

| 10.3    | Layer-merging of 16-bit and 32-bit Cooley-Tukey FFT                                                                                                      | 166 |

| Chanter | 12: Dilithium                                                                                                                                            | 183 |

|         |                                                                                                                                                          |     |

xxii LIST OF TABLES

|     | $12.1 \\ 12.2$ | Dilithium parameters [ABD <sup>+</sup> 20a] relevant to this work Relations between the quality $\theta$ of variants of Barrett multi-       | 183 |

|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     |                | plications and the modulus $q$                                                                                                               | 187 |

|     | 12.3           | Lower bounds on the modulus implementing the challenge polynomial multiplications in Dilithium with modulus switching.                       | 188 |

|     | 12.4           | Overview of the design space of challenge polynomial multiplications in Dilithium                                                            | 188 |

|     | 12.5           | Performance cycles of Dilithium NTTs and NTT <sup>-1</sup> s on Cortex-M3                                                                    | 189 |

|     | 12.6           | Performance cycles of Dilithium matrix-vector multiplications and size- $\ell$ inner products on Cortex-M3                                   | 190 |

|     | 12.7           | Performance cycles of polynomial multiplications with 16-bit arithmetic precision on Cortex-M3                                               | 191 |

|     | 12.8           | Performance cycles of polynomial multiplications with 32-bit                                                                                 |     |

|     | 12.9           | arithmetic precision on Cortex-M3                                                                                                            | 191 |

|     |                | in Dilithium on Cortex-M3                                                                                                                    | 192 |

|     |                | Performance cycles of Dilithium on Cortex-M3                                                                                                 | 193 |

|     | 12.11          | Performance cycles of Dilithium NTTs and NTT <sup>-1</sup> s on Cortex-M4                                                                    | 194 |

|     | 12.12          | Performance cycles of Dilithium matrix-vector multiplications and size- $\ell$ inner products on Cortex-M4                                   | 194 |

|     | 12.13          | Performance cycles of challenge polynomial multiplications $c\mathbf{s}_1$ and $c\mathbf{s}_2$                                               | 194 |

|     | 12.14          | Performance cycles of Dilithium on Cortex-M4                                                                                                 | 195 |

|     |                | Performance cycles of Dilithium NTTs and NTT <sup>-1</sup> s with Armv8-A Neon on Cortex-A72 and Firestorm                                   | 195 |

|     | 12.16          | Performance cycles of Dilithium matrix-vector multiplications and inner products with Armv8-A Neon on Cortex-A72 and                         | 190 |

|     |                | Firestorm.                                                                                                                                   | 196 |

|     | 12.17          | Performance cycles of Dilithium with Armv8-A Neon on                                                                                         | 100 |

|     | 12.11          | Cortex-A72 and Firestorm.                                                                                                                    | 197 |

|     | 12.18          | Performance cycles of Dilithium NTT/NTT <sup>-1</sup> , matrix-vector multiplications, and size- $\ell$ inner products with AVX2 on Haswell. |     |

|     | 12.19          | Performance cycles of Dilithium with AVX2 on Haswell                                                                                         | 198 |

| Cha | apter :        | 13: Kyber                                                                                                                                    | 199 |

|     | -              |                                                                                                                                              |     |

|     | 13.1           | Kyber parameter sets                                                                                                                         | 199 |

LIST OF TABLES xxiii

|   | 13.2           | Performance cycles of NTT and NTT <sup>-1</sup> in Kyber on Cortex-M3.   | 203 |

|---|----------------|--------------------------------------------------------------------------|-----|

|   | 13.3           | Performance cycles of matrix-vector multiplications and inner            |     |

|   |                | products in Kyber on Cortex-M3.                                          | 204 |

|   | 13.4           | Performance cycles of $Compress_d$ in Kyber on Cortex-M3                 | 205 |

|   | 13.5           | Performance cycles of Kyber on Cortex-M3                                 | 205 |

|   | 13.6           | Performance cycles of NTT and NTT <sup>-1</sup> in Kyber on Cortex-M4.   | 206 |

|   | 13.7           | Performance cycles of matrix-vector multiplications and inner            |     |

|   |                | products in Kyber on Cortex-M4.                                          | 207 |

|   | 13.8           | Performance cycles of Compress, in Kyber on Cortex-M4                    | 207 |

|   | 13.9           | Performance cycles of Kyber on Cortex-M4                                 | 208 |

|   | 13.10          | Performance cycles of NTTs and NTT <sup>-1</sup> s in Kyber with         |     |

|   |                | Armv8-A Neon on Cortex-A72 and Firestorm                                 | 209 |

|   | 13.11          | Performance cycles of matrix-vector multiplications and inner            |     |

|   |                | products in Kyber with Armv8-A Neon on Cortex-A72 and                    |     |

|   |                | Firestorm.                                                               | 210 |

|   | 13.12          | Performance cycles of C implementations of $\mathtt{Compress}_d$ in Ky-  |     |

|   |                | ber on Cortex-A72 and Firestorm                                          | 211 |

|   | 13.13          | Performance cycles of Armv8-A Neon implementations $\mathtt{Compress}_d$ |     |

|   |                | in Kyber on Cortex-A72 and Firestorm                                     | 212 |

|   | 13.14          | Performance cycles of Kyber with Armv8-A Neon on                         |     |

|   |                | Cortex-A72 and Firestorm                                                 | 213 |

|   | 13.15          | Performance cycles of NTT, NTT <sup>-1</sup> , and base multiplications  |     |

|   |                | of Kyber with AVX2 on Haswell                                            | 214 |

|   | 13.16          | Performance cycles of matrix-vector multiplications and inner            |     |

|   |                | products in Kyber with AVX2 on Haswell                                   | 214 |

|   | 13.17          | Performance cycles of C implementations of $Compress_d$ in Ky-           |     |

|   |                | ber on Haswell.                                                          | 215 |

|   | 13.18          | Performance cycles of AVX2 implementations of $\mathtt{Compress}_d$ in   |     |

|   | 40.40          | Kyber on Haswell                                                         | 215 |

|   | 13.19          | Performance cycles of Kyber with AVX2 on Haswell                         | 216 |

| C | hapter         | 14: NTRU                                                                 | 217 |

|   | 14.1           | NTRU parameter sets                                                      | 217 |

|   | $14.1 \\ 14.2$ | Performance cycles of polynomial multiplications in                      | 411 |

|   | 14.4           | ntruhps2048677 and ntruhrss701 on Cortex-M4                              | 225 |

|   | 14.3           | Performance cycles of ntruhps2048677 and ntruhrss701 on                  | 220 |

|   | 14.0           | Cortex-M4                                                                | 225 |

|   |                | 001001111111111111111111111111111111111                                  | 220 |

xxiv LIST OF TABLES

|     | 14.4   | Performance cycles of polynomial multiplications in<br>ntruhps2048677 and ntruhrss701 with Armv8-A Neon on                        |     |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

|     |        | Cortex-A72 and Firestorm.                                                                                                         | 226 |

|     | 14.5   | Performance cycles of polynomial inversions in $S_2, S_3$ , and $S_q$ of ntruhps2048677 and ntruhrss701 with Armv8-A Neon on      | 220 |

|     |        | Cortex-A72 and Firestorm.                                                                                                         | 227 |

|     | 14.6   | Performance cycles of ntruhps2048677 with Armv8-A Neon on                                                                         |     |

|     |        | Cortex-A72 and Firestorm.                                                                                                         | 228 |

|     | 14.7   | Performance cycles of ntruhrss701 with Armv8-A Neon on                                                                            |     |

|     |        | Cortex-A72 and Firestorm.                                                                                                         | 229 |

|     | 14.8   | Performance cycles of polynomial multiplications for NTRU                                                                         |     |

|     |        | with AVX2 on Skylake                                                                                                              | 229 |

|     | 14.9   | Performance cycles of NTRU with AVX2 on Skylake                                                                                   | 230 |

| CI  | antor  | 15: NTRU Prime                                                                                                                    | 231 |

| OI. | lapter | 15. WIIIO Time                                                                                                                    | 201 |

|     | 15.1   | Streamlined NTRU Prime parameter sets                                                                                             | 231 |

|     | 15.2   | NTRU LPrime parameter sets                                                                                                        | 233 |

|     | 15.3   | Performance cycles of polynomial multiplications in sntrup761                                                                     |     |

|     |        | on Cortex-M4                                                                                                                      | 237 |

|     | 15.4   | Performance cycles of sntrup761 on Cortex-M4                                                                                      | 238 |

|     | 15.5   | Approaches for computing a size-1536 product with radix-2                                                                         |     |

|     |        | Schönhage                                                                                                                         | 240 |

|     | 15.6   | Approaches for multiplying polynomials in $\mathbb{Z}_q[x]/\langle x^{64}+1\rangle$ and $\mathbb{Z}_q[x]/\langle x^{32}+1\rangle$ | 243 |

|     | 15.7   | Performance cycles of polynomial multiplications over $\mathbb{Z}_q$ in                                                           |     |

|     |        | sntrup761 with Armv8-A Neon on Cortex-A72 and Firestorm.                                                                          | 246 |

|     | 15.8   | Performance cycles of polynomial inversion over $\mathbb{Z}_3$ in sntrup761                                                       |     |

|     |        | with Armv8-A Neon on Cortex-A72 and Firestorm                                                                                     | 247 |

|     | 15.9   | Performance cycles of sntrup761 with Armv8-A Neon on                                                                              |     |

|     |        | Cortex-A72 and Firestorm                                                                                                          | 248 |

|     | 15.10  |                                                                                                                                   |     |

|     |        | sntrup761 with AVX2 on Haswell and Skylake                                                                                        | 250 |

|     | 15.11  | 1                                                                                                                                 |     |

|     |        | Skylake                                                                                                                           | 250 |

| Cł  | apter  | 16: Saber                                                                                                                         | 251 |

|     | 16.1   | Saher narameter sets                                                                                                              | 951 |

|     |        |                                                                                                                                   |     |

| LIST OF | F TABLES | XXV |

|---------|----------|-----|

|         |          |     |

| 16.2           | Performance cycles of polynomial multiplications in Saber on                           | 050        |

|----------------|----------------------------------------------------------------------------------------|------------|

| 16.3           | Cortex-M3                                                                              | 258        |

| 16.4           | products in Saber on Cortex-M3                                                         | 259<br>260 |

| $16.4 \\ 16.5$ | Performance cycles of polynomial multiplications in Saber on                           | 200        |

| 10.5           | Cortex-M4                                                                              | 261        |

| 16.6           | Performance cycles of polynomial multiplications with 32-bit NTT in Saber on Cortex-M4 | 262        |

| 16.7           | Performance cycles of matrix-vector multiplications and inner                          |            |

|                | products in Saber on Cortex-M4                                                         | 262        |

| 16.8           | Performance cycles of Saber on Cortex-M4                                               | 263        |

| 16.9           | NTT and NTT <sup>-1</sup> for Saber with Armv8-A Neon on Cortex-A72                    |            |

| 10.10          | and Firestorm                                                                          | 264        |

| 16.10          | Performance cycles of matrix-vector multiplications and inner                          |            |

|                | products in Saber with Armv8-A Neon on Cortex-A72 and Firestorm.                       | 005        |

| 16 11          | Performance cycles of Saber with Armv8-A Neon on                                       | 265        |

| 10.11          | Cortex-A72 and Firestorm                                                               | 266        |

| 16.12          | Performance cycles of 16-bit NTT and NTT <sup>-1</sup> for Saber with                  | 200        |

| 10.12          | AVX2 on Haswell                                                                        | 267        |

| 16.13          | Performance cycles of matrix-vector multiplications and inner                          |            |

|                | products in Saber with AVX2 on Haswell                                                 | 267        |

| 16.14          | Performance cycles of Saber with AVX2 on Haswell                                       | 268        |

| Chapter        | A: On Formal Verification                                                              | 293        |

| A.1            | Verification time of range conditions for a size-1024 complex                          |            |

|                | FFT                                                                                    | 306        |

| A.2            | Verification time of equivalence proofs between Armv7-M im-                            |            |

|                | plementations and our CryptoLine models                                                | 308        |

| A.3            | Kyber parameter sets                                                                   | 315        |

| A.4            | Saber parameter sets                                                                   | 315        |

| A.5            | NTRU parameter sets                                                                    | 316        |

| A.6            | Verification results (in seconds)                                                      | 349        |

| Chapter        | B: Large Integer Multiplications                                                       | 353        |

| B.1            | Parameters of NTT multiplications for RSA                                              | 366        |

xxvi LIST OF TABLES

| B.2 | Performance cycles of our Cortex-M3 NTTs and FNTs in cycles.  | 371 |

|-----|---------------------------------------------------------------|-----|

| B.3 | Performance cycles of our Cortex-M55 NTTs and FNTs in cycles. | 371 |

| B.4 | Performance cycles of modular multiplication, squaring, expo- |     |

|     | nentiation in cycles on Cortex-M3 and Cortex-M55              | 372 |

| B.5 | Performance cycles of Hensel lifting on Cortex-M3 and         |     |

|     | Cortex-M55                                                    | 375 |

| B.6 | Performance monitoring unit statistics for Cortex-M55 imple-  |     |

|     | mentations.                                                   | 378 |

### Chapter 1

### Introduction

The process of preparing programs for a digital computer is especially attractive, not only because it can be economically and scientifically rewarding, but also because it can be an aesthetic experience much like composing poetry or music.

Donald E. Knuth, Fundamental Algorithms Volume 1 of The Art of Computer Programming

### 1.1 Subject of Research

Cryptography studies how secure communications can be established under various adversarial models and real-world attacks.

Symmetric cryptography and asymmetric cryptography. There are two major lines of cryptography: symmetric cryptography and asymmetric cryptography. In symmetric cryptography, all the parties hold the same secret key and transform the plaintext into ciphertext and ciphertext into plaintext with the secret key or procedures derived from the secret key. This allows parties sharing a secret key to transfer large chunk of confidential data through insecure channels by transforming plaintext back-and-forth. Asymmetric cryptography removes the need of sharing the secret key among parties.

**Post-quantum cryptosystems.** Although large-scale cryptanalytic-relevant quantum computers are not yet available, some secret information nowadays is

susceptible to attacks by future quantum computers. For an encryption cryptosystem, an attacker stores the public information, and extracts the secret key and decrypts the ciphertext once large-scale quantum computers are available. For symmetric cryptography, Grover's algorithm reduces the brute-force search bit-complexity by half in quantum computation model [Gro96], and doubling the key size is sufficient to achieve comparable security. However, things are quite different for asymmetric cryptography. Popular approaches such as Rivest-Shamir-Adleman relying on the hardness of integer factorization and elliptic-curve cryptography relying on the hardness of elliptic-curve discrete logarithm are broken by Shor's algorithms in quantum computation model [Sho97a]. Post-quantum cryptography studies cryptosystems relying on hard problems that are believed to be secure against quantum computers. There are five major lines of post-quantum cryptosystems in post-quantum cryptography: lattice-based cryptosystems, multivariate cryptosystems, hashbased cryptosystems, code-based cryptosystems, and isogeny-based cryptosystems.

NIST Post-Quantum Cryptography Standardization. At PQCrypto 2016, the National Institute of Standards and Technology (NIST) initiated the Post-Quantum Cryptography Standardization with multi-round evaluation, soliciting post-quantum cryptography schemes implementing key-encapsulation mechanisms (KEMs) and digital signatures. NIST received 82 candidates, and 69 candidates were regarded complete and participated the first-round evaluation. Lattice-based cryptosystems are among the most popular constructions due to their well-balanced performance in terms of the amount of data to be transmitted and the processing time. Indeed, NIST advanced 26 submissions to round two on January 30th, 2019, and among the 26 candidates, 12 were lattice-based, 7 were code-based, 1 was hash-based, 4 were multivariatebased, 1 was super-singular-isogeny-based, and 1 was zero-knowledge-proofbased [AASA<sup>+</sup>19]. NIST advanced 15 candidates to round three on July 22nd, 2020 [AASA<sup>+</sup>20] and 7 of them were lattice-based cryptosystems. On July 5th, 2022, NIST selected 5 cryptosystems as the first group of cryptosystems for standardization [AAC<sup>+</sup>22] and 3 were lattice-based. NIST also moved 4 candidates to round four and one of the candidates was broken in round four. On March 11th, 2025, NIST selected a candidate for standardization from round four  $[ABC^+25]$ .

### 1.1.1 Lattice-Based Cryptosystems and Platforms

In a typical lattice-based cryptosystem, one of the computational bottlenecks is polynomial arithmetic such as polynomial multiplications over integer rings, matrix multiplications over integer rings, and matrix-to-vector multiplications over polynomial rings. This thesis reviews and improves the software implementations of polynomial arithmetic in five out of the seven lattice-based cryptosystems in the third round of NIST PQC Standardization on five platforms. For the lattice-based cryptosystems, this thesis looks into Dilithium, Kyber, NTRU, NTRU Prime, and Saber (in alphabetical order). As for the platforms, this thesis focuses on Cortex-M3 implementing Armv7-M, Cortex-M4 implementing Armv7E-M, Cortex-A72 implementing Armv8.0-A, Firestorm implementing Armv8.4-A, and Haswell implementing x86-64 with AVX2. See Tables 1.1 and 1.2 for an overview.

Cortex-M3 Cortex-M4 Cryptosystem Armv7-M Armv7E-M Dilithium Reviewing/improving. Reviewing/improving. Kvber Reviewing/improving. Reviewing/improving. NTRU Reviewing. NTRU Prime Reviewing. Saber Reviewing/improving. Reviewing.

Table 1.1: Scope of this thesis on Cortex-M3 and Cortex-M4.

Table 1.2: Scope of this thesis on Cortex-A72, Firestorm, and Haswell.

| Cryptosystem | Cortex-A72/Firestorm | Haswell              |

|--------------|----------------------|----------------------|

|              | Armv8.0-A/Armv8.4-A  | x86-64 with AVX2     |

| Dilithium    | Reviewing/improving. | Reviewing.           |

| Kyber        | Reviewing/improving. | Reviewing/improving. |

| NTRU         | Reviewing/improving. | Reviewing.           |

| NTRU Prime   | Reviewing/improving. | Reviewing/improving. |

| Saber        | Reviewing.           | Reviewing.           |

### 1.1.2 Assembly

We specifically focus on assembly-optimized implementations for the performance-critical polynomial arithmetic in lattice-based cryptosystems. Natural concerns are the engineering effort, maintainability, and portability of assembly-optimized implementations. Maintainability heavily depends on the programming practice and varies a lot between programmers. It is true that programming directly in assembly amounts to huge engineering effort and suffers from portability across different architectures. However, there are several issues if we do not have fine-grained control on the assembly, and the benefit of programming in assembly payoff if we focus on the performance-critical component. We outline below the implementation challenges.

Secret-independent execution time. A function has secret-independent execution time<sup>1</sup> if the execution time is independent from the secret inputs. There are at least three possible sources of secret-dependent execution time – conditional branches, memory access patterns, and assembly instructions. If the condition of a conditional branch is evaluated differently for different secret inputs, then the computational flows will be different and often lead to different execution time. If the memory location to be accessed varies for different secret inputs, we could possibly hit cache misses for some inputs and end up spending more time loading from memory for some secret inputs. At the assembly-instruction level, there are some instructions whose execution time depend on the secret inputs. When any of these occurs, the attacker learns some information on the secret inputs. A straightforward countermeasure is to implement functions with secret inputs with carefully selected assembly instructions, so compilers have no chances to replace the secret-independent computations with the often faster secret-dependent computations.

Same instructions, different platforms. When executing a function, the optimization strategies might be quite different on different platforms. For example, while copying an array of elements to another array on Cortex-M4 and Cortex-M7 both implementing the instruction set architecture Armv7E-M, grouping the loads together and the stores together is faster on a Cortex-

<sup>&</sup>lt;sup>1</sup>Secret-independent execution time is also called constant-time. However, the term constant-time does not necessarily mean constant execution time. Computations on the public do not need to run in constant execution time. If the overall computation has variable execution time and the computations on secret data has constant execution time, we also call it constant-time. However, the term constant-time does not align well with the common usage of constant-time and this thesis deliberately chooses secret-independent execution time to avoid this.

M4 processor while interleaving the loads and stores is faster on a Cortex-M7 processor. Programing in assembly gives us full control over instruction scheduling.

Same platform, compiler, and code, different compilation flags. On the same platform and with the same compiler, the same program might be compiled into different assembly programs if we change the compilation flags. For example, the C operator % is compiled into division, multiplication, and subtraction with optimization flag -00, and sometimes into a string of instructions excluding divisions with -03 [Dan24]. As the execution time of division instructions often depend on the inputs, it is best to avoid them. A straightforward way is to replace the % operator with a string of assembly instructions without divisions.

**Support of vector instructions.** Vector instructions are now commonly implemented on high-performance processors. From the programming point of view, a batch of arithmetic of the same kind is packed as a single instruction, allowing us to issue a batch of computations with small instruction-decoding bandwidth. While auto-vectorization is a common compiler optimization, programming in assembly ensures the desired vectorization.

Same platform and compiler, different code structure. Intrinsics are architecture-specific functions/macros allowing programmers to access the low-level special assembly instructions in a high-level programming language. However, the mapping between intrinsics and assembly instructions are not necessarily uniquely determined. We illustrate an example with matrix multiplications. Let I, J, K be positive integers that are multiples of four. Given matrices  $A \in M_{I \times J}(\mathbb{Z}_{2^{32}})$ ,  $B \in M_{J \times K}(\mathbb{Z}_{2^{32}})$ ,  $C \in M_{I \times K}(\mathbb{Z}_{2^{32}})$ , we wish to compute AB + C over  $\mathbb{Z}_{2^{32}}$ . The computing task is named as "matrix multiplication with accumulation of dimension  $I \times J \times K$ ." Listing 1.1 is a C implementation iterating in the order i, j, k with  $\mathbb{Z}_{2^{32}}$  encoded as int32\_t.

Listing 1.1: Matrix multiplication with accumulation of dimension  $I \times J \times K$ .

```

void matmla_ijk_int32(int32_t *C, const int32_t *A, const

int32_t * B){

// A: I by J

// B: J by K

// C: I by K

for(size_t i = 0; i < I; i++){

for(size_t j = 0; j < J; j++){</pre>

```

On Armv8-A Neon, a vector instruction set comes with the Armv8-A instruction set architecture, there are vector loads, stores, and multiplications with accumulations. There are two kinds of multiplications: vector-by-vector and vector-by-scalar. A vector-by-vector multiplication component-wisely multiplies the elements of two vectors, and a vector-by-scalar multiplication multiplies the scalar operand to each of the elements of the vector operand. We again iterate in the order i,j,k and rewrite the inner loops with vector loads, stores, and vector-by-scalar multiplications in intrinsics as shown in Listing 1.2. On an Apple M1 Pro running Sonoma 14.6.1, the inner loops are compiled into vector duplications and vector-by-vector multiplications in assembly with the compiler Apple clang version 15.0.0 and optimization flags -03 -march=native. If we instead iterate in the order i,k,j as shown in Listing 1.3, the inner loops are compiled into vector-by-scalar multiplications as expected. Programming in assembly gives us full control on instruction selections and we do not need to rely on compilers to select the desired instructions.

Listing 1.2: Matrix multiplication with accumulation of dimension  $I \times J \times K$  iterating in the order i, j, k with Armv8-A Neon intrinsics in C.

```

void matmla_ijk_lane_int32(int32_t *C, const int32_t *A, const

int32_t * B){

int32x4_t cx4, ax4, bx4[4];

for(size_t i = 0; i < I; i++){

for(size_t j = 0; j < J; j += 4){

ax4 = vld1q_s32(A + i * J + j);

for(size_t k = 0; k < K; k += 4){

bx4[0] = vld1q_s32(B + (j + 0) * K + k);

bx4[1] = vld1q_s32(B + (j + 1) * K + k);

bx4[2] = vld1q_s32(B + (j + 2) * K + k);

bx4[3] = vld1q_s32(B + (j + 3) * K + k);

/* Below are compiled into duplications and

vector-by-vector multiplications. */

cx4 = vmlaq_laneq_s32(cx4, bx4[0], ax4, 0);

cx4 = vmlaq_laneq_s32(cx4, bx4[1], ax4, 1);

cx4 = vmlaq_laneq_s32(cx4, bx4[2], ax4, 2);

cx4 = vmlaq_laneq_s32(cx4, bx4[3], ax4, 3);

```

```

vst1q_s32(C + i * K + k, cx4);

}

}

}

```

Listing 1.3: Matrix multiplication with accumulation of dimension  $I \times J \times K$  iterating in the order i, k, j with Armv8-A Neon intrinsics in C.

```

void matmla_ikj_lane_int32(int32_t *C, const int32_t *A, const

int32_t * B){

int32x4_t cx4, ax4, bx4[4];

for(size_t i = 0; i < I; i++){

for(size_t k = 0; k < K; k += 4){

cx4 = vld1q_s32(C + i * K + k);

for(size_t j = 0; j < J; j += 4){

ax4 = vld1q_s32(A + i * J + j);

bx4[0] = vld1q_s32(B + (j + 0) * K + k);

bx4[1] = vld1q_s32(B + (j + 1) * K + k);

bx4[2] = vld1q_s32(B + (j + 2) * K + k);

bx4[3] = vld1q_s32(B + (j + 3) * K + k);

/* Below are compiled into vector-by-scalar

multiplications. */

cx4 = vmlaq_laneq_s32(cx4, bx4[0], ax4, 0);

cx4 = vmlaq_laneq_s32(cx4, bx4[1], ax4, 1);

cx4 = vmlaq_laneq_s32(cx4, bx4[2], ax4, 2);

cx4 = vmlaq_laneq_s32(cx4, bx4[3], ax4, 3);

vst1q_s32(C + i * K + k, cx4);

}

}

}

```

### 1.2 Contributions of This Thesis

#### 1.2.1 Microcontrollers

On microcontrollers, the first two publications were published when I was an undergraduate student at National Taiwan University. According to the

regulations of National Taiwan University, only publications published after the start date of a master's program are allowed to be included in the master's thesis. Therefore, the first two publications were not included in my master thesis and they are included as contributions of this thesis.

Polynomial multiplications for NTRU Prime on Cortex-M4. The first contribution targets the polynomial multiplications for NTRU Prime on Cortex-M4, and is based on the following published work.

Erdem Alkim, Dean Yun-Li Cheng, Chi-Ming Marvin Chung, Hülya Evkan, Leo Wei-Lun Huang, Vincent Hwang, Ching-Lin Trista Li, Ruben Niederhagen, Cheng-Jhih Shih, Julian Wälde, and Bo-Yin Yang. Polynomial Multiplication in NTRU Prime: Comparison of Optimization Strategies on Cortex-M4. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2021(1):217–238, 2020. Paper. Artifact. Talk. Slides. IACR ePrint. Reference [ACC+20].

**Summary:** We proposed three assembly-optimized NTT-based implementations for the polynomial multiplication in NTRU Prime on Cortex-M4. I was deeply involved in the Good–Thomas implementation.

We explored several polynomial multiplication strategies, including Good—Thomas FFT, Rader-17 FFT, and Cooley—Tukey FFT, Toom—Cook, and several implementation techniques, such as the uses of floating-point registers as low-latency cache and multi-layer butterflies to reduce the memory operations. We chose a 32-bit NTT-friendly modulus and applied Good—Thomas and Cooley—Tukey FFTs with the 32-bit Montgomery multiplication using 32-bit multiplication instructions. We also proposed three implementations exploiting the 16-bit Digital Signal Processing multiplication instructions: Toom—Cook, mixed-radix with small radices, and Rader-17. I was deeply involved in the development of Good—Thomas FFT and Cooley—Tukey FFT implementations.

Polynomial multiplications for NTRU, Saber, and LAC on Cortex-M4 and Skylake. The second contribution targets the polynomial multiplications for NTRU, Saber, and LAC on Cortex-M4 and Skylake, and is based on the following published work.

Chi-Ming Marvin Chung, Vincent Hwang, Matthias J. Kannwischer, Gregor Seiler, Cheng-Jhih Shih, and Bo-Yin Yang. NTT

Multiplication for NTT-unfriendly Rings: New Speed Records for Saber and NTRU on Cortex-M4 and AVX2. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2021(2):159–188, 2021. Paper. Artifact. Talk. Slides. IACR ePrint. Reference [CHK<sup>+</sup>21].